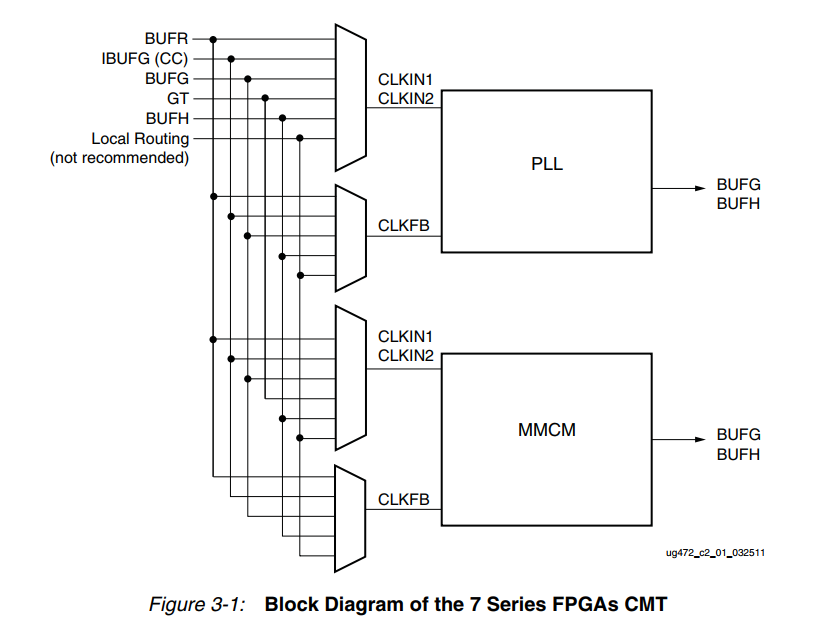

CMT是非常重要的时钟资源,如果时钟信号像血液的话,CMT就像是循环系统,MRCC和SRCC将外部时钟引入,但是需要经过处理才能被其他部件所使用。时钟信号在运行过程中,还会发生各种负面的变化,例如jitter(抖动)时钟频率发生变化,偏移(到达不同部件时间不同)和占空比失真(一个周期内部不对称)。从CMT(Clock Management Tile)的名字也可以看出来。一个CMT包括了一个MMCM(Mixed-mode Clock Manager)和一个PLL(Phase-locked loop)。PLL的功能是MMCM的一个子集。MMCM的上一代就叫做DCM(digital clock manager)。下图是CMT支持的输出输出。

7系列的设备支持最多24个CMT,MMCM和PLL可以用作频率合成器,去抖动和偏斜。7系列的PLL是基于MMCM简化设计的,而并非上一代PLL的升级。MMCM的额外功能有

通过CLKOUT[0:3]直连BUFR或者BUFIO的HPC(high performance clock)

时钟反向输出(CLKOUT[0:3]B)

CLKOUT6

CLKOUT4_CASCADE (级联)

Fractional divide for CLKOUT0_DIVIDE_F (分频)

Fractional multiply for CLKFBOUT_MULT_F (倍频)

Fine phase shifting (精细相移)

Dynamic phase shifting (动态相移)

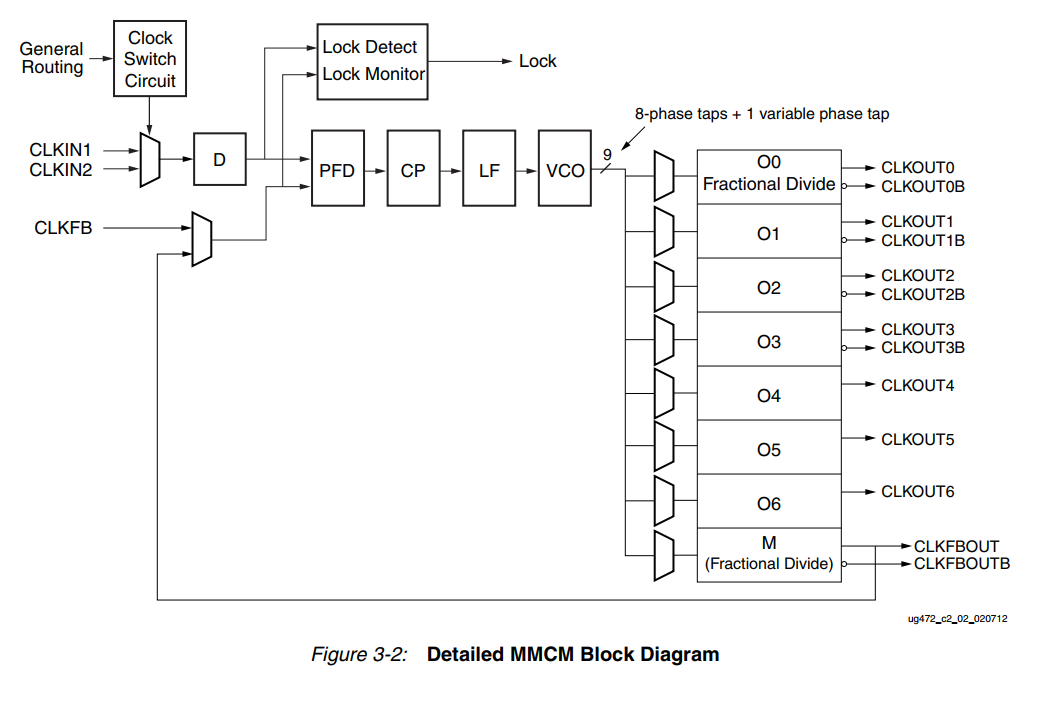

以下是MMCM的结构图

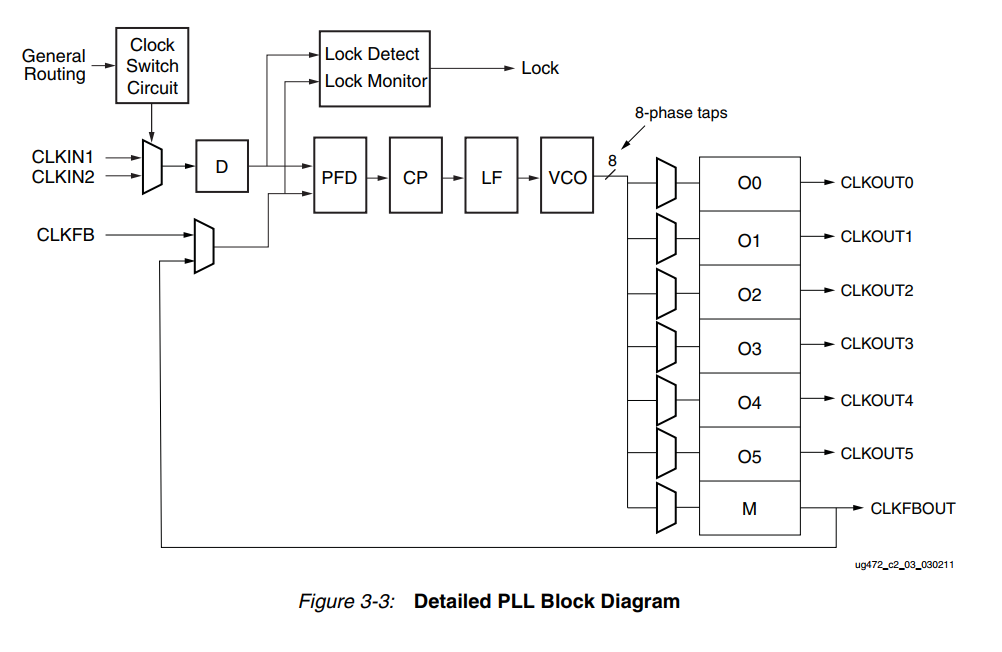

输入多路复用器从IBUFG,BUFG,BUFR,BUFH,GT(仅CLKIN)或interconnect(不推荐)中选择参考时钟和反馈时钟。每个时钟输入都有一个可编程的计数器分频器(D)。相频检测器(PFD)比较输入(参考)时钟和反馈时钟的上升沿的相位和频率。If a minimum High/Low pulse is maintained, the duty cycle is ancillary ? PFD用于生成与两个时钟范围内的相位和频率成比例的信号。该信号驱动Charge pump(CP)和loop filter(LF)生成VCO的参考电压。PFD会向电荷泵和环路滤波器产生一个上升或下降信号,以确定VCO应该以更高还是更低的频率工作。当VCO的频率过高时,PFD会激活一个下降信号,从而导致控制电压降低,从而降低VCO的工作频率。当VCO的频率太低时,上升信号将增加电压。 VCO产生八个输出相位和一个可变相位以实现精细相移。每个输出相位都可以作为输出计数器的参考时钟。每个计数器都可以独立编程。为了实现频率合成,还额外提供了一个M,这个计数器负责控制反馈时钟。另外除了整数倍的分频输出计数,MMCM还为CLKOUT0和CLKBOUT增加了分数计数器。下图书PLL的详细结构图。

比较之后可以发现,大体结构相同,区别在于:

没有CLKOUT[0:3]B,反相输出

只有八个输出相位,没有可变相位,无法实现精细相移

没有分数计数器,无法实现分数倍频率合成

少一个CLKOUT6

接下来是MMCM和PLL的一般用法

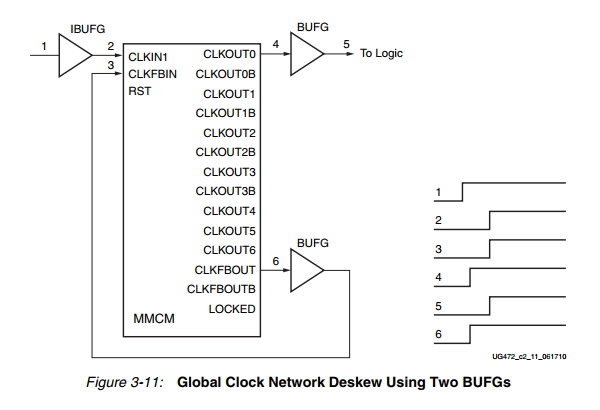

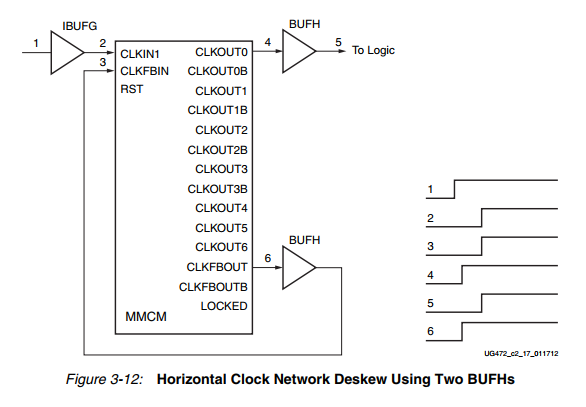

从图的名字也可以看出来这是用了两个BUFG来去除时钟网络的偏移。一个CLKOUT用来驱动逻辑资源,而另一个反馈时钟用来精确控制输出和输出时钟之间的相位关系,右边的波形图展示了输入和输出需要相位对齐时的情况。

上图是全局时钟,下图是用BUFH做的。

当MMCM被用作频率合成和抖动过滤并且对输出和输入的相位没有要求时,可以用内部信号作为反馈信号。此时MMCM的性能会更好,因为反馈时钟没有经过其他电源供电的元件,因此也就没有其他电源的噪声。但是从CLKIN和BUFG的噪声还是照常。

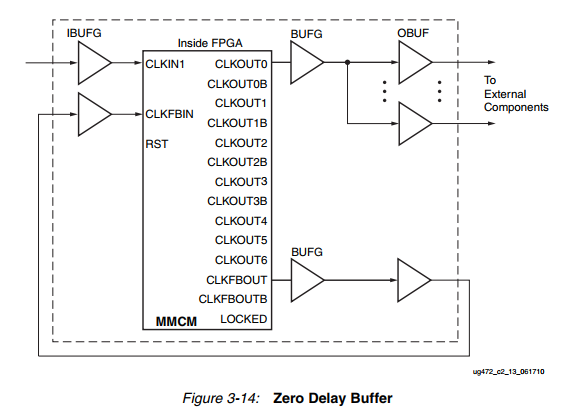

MMCM也能被用来生成一个无延迟的buffer clcok, 如下图。无延迟的buffer可以吧一个时钟信号扇出给多个目的地,并且信号之间的偏移很小。

该设计主要是反馈信号的延迟要和输出信号一致,反馈信号要匹配输出信号,从而使得CLKIN和CLKBIN的相位一致。但是有时候输出信号路线上的电容和反馈路线上的电容不一样大,这样的话信号边沿的斜率就会不同。